2023太原站wtt常规挑战赛比赛时间是从11月7日开始吗?

2023-10-30

更新时间:2023-10-23 14:09:10作者:橙橘网

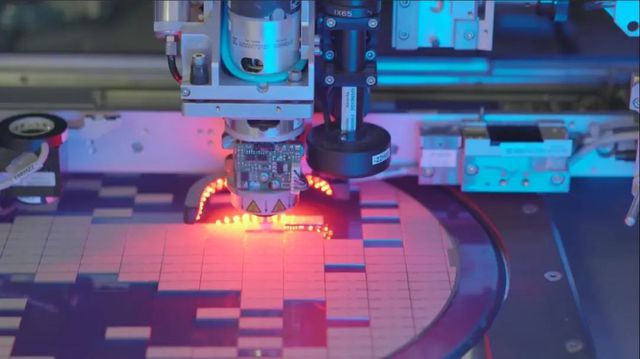

最近,芯片圈儿又有大新闻了。

佳能搞出了个新的芯片制造设备,不用光刻技术,就能造 5nm 的芯片。

而且说是再优化优化, 2nm 制程也不是啥大问题。

这可先把一众网友们搞懵圈儿了,佳能怎么不好好造相机,跑出来搞造芯片的机器了?

并且一出手就是 5nm 、 2nm 的。

而这,差评君就不得不先帮佳能找补几句了,其实一直以来,佳能在芯片制造设备上都有布局,隔壁的尼康也是一个样。

不过目前光刻机的顶尖技术一直都被 ASML 独占,佳能眼看追不上,于是在研究光刻机的同时,又找了另外一条赛道:纳米压印。

这次新闻的主角,也正是这个 “ 纳米压印 ” 技术,反正消息一出,吃瓜群众们的反应是最热烈的。

像是什么“ 光刻机即将被取代,纳米压印战未来 ” “ ASML 这下要慌了,被换赛道超车了 ” 。。。各种讨论看得人一片沸腾,好像光刻机这玩意儿,以后只能在废品回收站里看到了似的。

差评君也去大致了解了一下,却发现事情比想象中的复杂,且有趣。

首先这些年来,光刻机的发展已经逐渐走到一个瓶颈期,芯片制程的进步速度,也肉眼可见得变慢。

没有对比就没有伤害,反观发展至今才二十多年的纳米压印技术,却是一个 “ 快 ” 字了得,噌噌几年就快要赶上光刻机的进度了。

对比上个世纪五十年代起步的光刻技术,速度直接翻了一倍多。

并且,新的纳米压印技术和光刻机相比,不但成本也降了,甚至制造工艺也贼简单,更适合大规模生产。

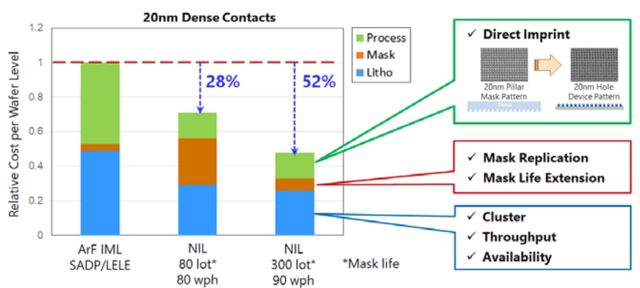

这么说吧,用光刻技术造芯片,总成本要是十块,光刻步骤就得花三块,时间成本也占到总成本的一半。

对比之下,用纳米压印技术可以省掉将近三成的成本,要是晶圆吞吐量再提升一点,直接就能节省一大半的成本。

更重要的是,纳米压印技术的工艺非常简单,跟盖章一样,像下图这种印章各位差友们应该都见过或者玩过吧。

纳米压印的原理呢,和它差不多,只不过是迷你微缩版。

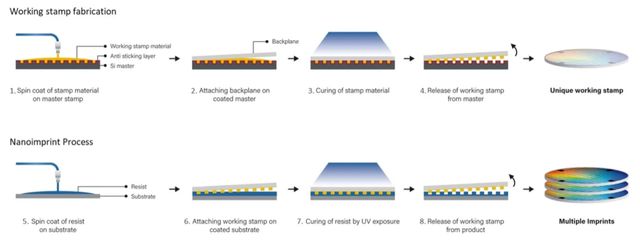

制造的过程统共就分两步,一步造 “ 印章 ” ,一步 “ 盖章 ” 。

先在刻好电路的底板上喷涂印章所需的材料,等凝固后就是纳米压印的印章。

然后再在晶片上喷涂一层纳米压印胶,直接盖章、等待凝固、脱模就 OK 了。

在造印章、盖章的过程中,都不用替换工具,一个 “ 喷头 ” 就能搞定,期间只需要更换里面的材料。

而隔壁需要折来折去的 EUV 光刻技术,不仅要一个庞大的透镜阵列来控制光线,并且要产生这个波长极短的极紫外光,还得大功率支撑着。

这样对比之下,纳米压印技术简直是集能耗小、工艺简单、设备轻便等优点于一身,不少人都认为这会是最有可能替代 EUV 光刻的技术。

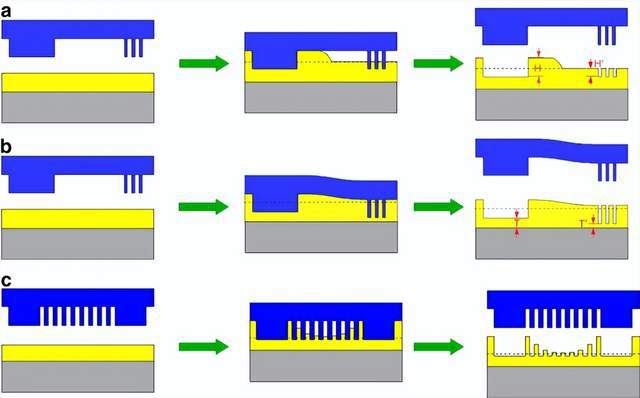

而且如今,纳米压印技术也已经发展出了不少分支,光是压印方式就有三种:热压印、紫外压印和微接触压印,其中紫外压印常用在芯片制造中,在紫外光的照射下,压印胶很容易凝固脱模。

根据固化方式、压印面积等分类也衍生出了很多不同的工艺。

这些工艺,除了造芯片之外,还能用在 LED 、 OLED 、 AR 设备中。

可以说,在纳米压印这块儿,已经有百花齐放,步入快车道的迹象了。

另外,整个芯片制造行业,对纳米压印技术的关注也不少。

从 2004 年开始,上面我们提到的佳能,就开始悄悄研究起了纳米压印。2014 年它收购了美国的一家纳米压印公司 Molecular Imprints( 分子压模 ),正式宣布进入纳米压印市场。

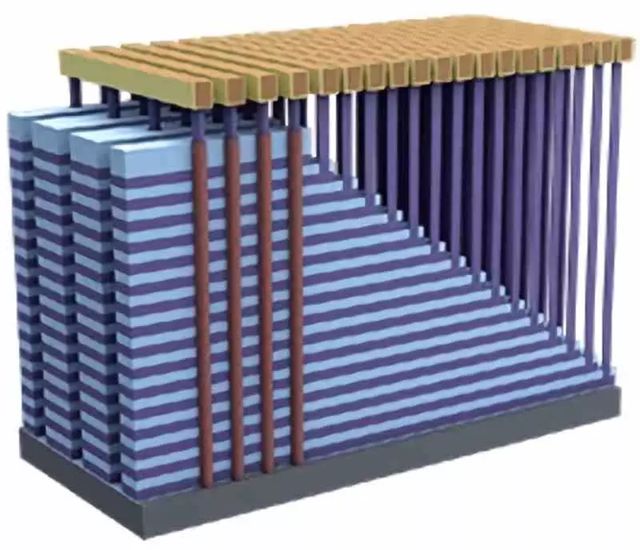

后来,它还和东芝( 现在的铠侠 )合作,准备用纳米压印技术造 3D NAND 闪存,三星在买 EUV 设备的同时,也还在着手进行纳米压印技术的研发。

就连 SK 海力士也从佳能那边买了纳米压印设备,准备搞 3D NAND 闪存生产测试,并计划在 2025 年实现大规模量产。

如果能顺利实现商业化的话,200 层以上的 3D NAND 闪存生产效率会大大提高。

到时候,用纳米压印技术造 DRAM 、 CPU 等芯片自然也就不远了。

在国内,纳米压印的市场也是发展得火热,不少高校像复旦、北大等都有相关的研究。前几天佳能官宣自家的纳米压印设备之后,还顺带拉动了国内相关概念股,汇创达盘中一度涨超 14% 。

国内的一些上市企业,比如美迪凯、奥比中光、腾景科技等也都在纳米压印相关行业有所布局,并且还在继续搞相关技术的研发。

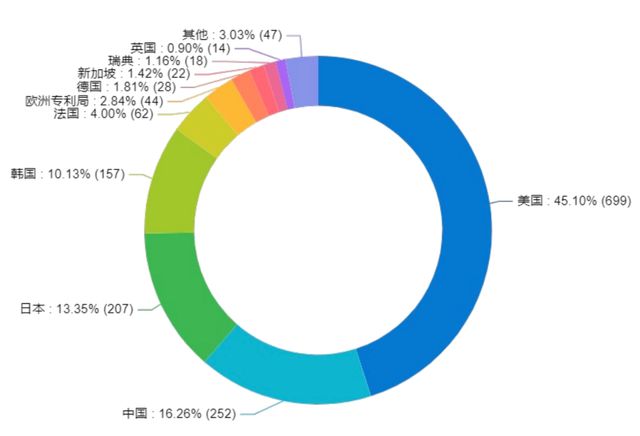

前期,市场火热最直观的体现就是在专利上,目前国内在纳米压印技术相关专利总数上排名第二,占比全球总数的 16% 。

所以说纳米压印技术,妥妥是目前的当红辣子鸡。

不过在差评君心里还有个疑团,纳米压印技术这么简单,一句话就能解释清楚原理,为啥这么晚才被研究,不应该早就应用了吗?

于是我又回过头仔细研究了下纳米压印的工艺流程,发现纳米压印这技术,在一开始就卡了个大 BUG 。

而这 BUG ,也算是解答了差评君的疑问,那就是:光刻机到底会不会被取代、被淘汰?

还拿盖印章的例子来说,用这种方法做芯片,第一步首先得做印章吧,但纳米压印做那个 “ 印章 ” 的模具是 1 :1 的。

但要怎么 “ 挖出 ” 印章里这种纳米级的沟道?

( 温馨提示:当初就是因为挖不出纳米级的沟道才搞出的光刻机,用 5 :1 甚至 10 :1 放大后的电路板光刻。 )

所以能供纳米压印选择的要么是光刻,要么就是实验室里的电子束曝光以及聚焦离子束。

emmm 合着这一圈儿又回到起点了。。。

不过好在那个做印章的 “ 模具 ” 可以重复使用,不用大量生产,也算是另一种方式的节省成本,不然真就是脱裤子放屁。

当然,除了这个大 BUG 外,纳米压印还有不少的技术难题等着解决。

平时我们自己玩印章的时候都避免不了印的不均匀,或者缺边少角的。

而在纳米尺度下的纳米压印技术,这些情况就更不能避免了,像下面这些两边高度不一、印章变形、没有完全契合的现象都是很常见的残次品。

要避免这些残次品的出现,就得在技术上下功夫。

首先就是喷涂过程,也就是在晶片上喷涂纳米压印胶,在这个过程中,喷涂的厚度、均匀度等都有着严格的要求,并且还不能有气泡、灰尘进入,一旦进入直接就报废了。。。

解决办法目前都是在压印过程下功夫,局部加热不均匀的部分,好让印章和印胶严密贴合。

还有就是脱模过程,为了能让压印胶更好的脱模,业内一般都会在胶上面搞上一层纳米级别的抗粘性材料。

这虽然好脱模了,但这种抗粘性材料还会和模具发生摩擦啥的,模具的寿命也会因此缩短。

另外还有压印胶材料、模具材料的选择,模具定位及套刻精度,精确控制等等一系列问题。

这些零碎的技术难题,体现到产品上就是良率的问题。

所以,要实现纳米压印芯片量产就绕不开这些问题,而要解决这些问题,大量的研发以及试错成本少不了,这一切,都需要时间来支撑。

最后,再回到开头说的纳米压印能不能取代光刻机的问题上。

相信看到这里的朋友们心里应该都有答案了:肯定不会,毕竟纳米压印在第一步就绕不开光刻技术。

更重要的是,差评君觉得,这两种技术之间的关系并不是非此即彼,与其说纳米压印会取代光刻机,不如说纳米压印是光刻技术的延伸。

就像二十世纪通用机床一样,一开始它们只生产产品,后来转向生产专用工具,专用工具再生产产品,不仅扩大了产能,还降低了成本。

或许未来有一天,光刻机也会迎来这样的角色转变,到时候,说不定芯片制造业,已经完成了新一轮的革新。