前海开源基金杨德龙:国新投资增持央企ETF有利于推动资本市场转暖

2023-12-02

更新时间:2023-11-07 12:05:29作者:橙橘网

本文系网易新闻•网易号特色内容激励计划签约账号【智东西】原创内容,未经账号授权,禁止随意转载。

作者 | 佳慧

编辑 | 云鹏

智东西11月6日报道,今晚七点,联发科技的天玑旗舰芯片新品发布会准时开始。

在发布会上,联发科正式发布了新一代旗舰5G生成式AI移动芯片天玑9300。并且据联发科官方介绍,此款芯片是全球首款全大核架构智能手机芯片。

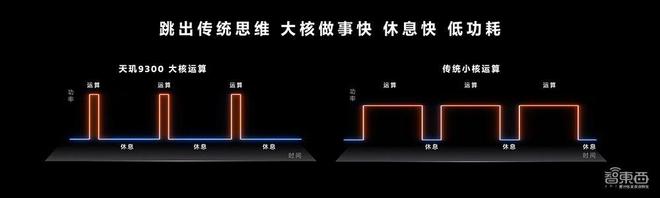

据介绍,天玑9300是4个超大核+4个大核架构,CPU包含4个Cortex-X4超大核,以及4个主频为2.0GHz的Cortex-A720大核,采用台积电新一代4nm工艺,有227亿晶体管,有8MB三级缓存和10MB系统缓存。与天玑9200相比,天玑9300的峰值性能提升40%,同性能下能耗下降33%。

在GPU上,天玑9300采用12核Immortalis-G720 MC12 1300MHz,与天玑9200相比,性能提升同能耗下46%,同性能下能耗下降40%。

一、集成第七代AI处理器,内置生成式AI引擎

天玑9300集成联发科技第七代AI处理器APU 790。APU 790内置生成式AI引擎,与Transformer模型适配进行算子加速,处理速度是天玑9200的8倍,可以实现1秒内生成图片。

结合内存硬件压缩技术NeuroPilot Compression来减少AI大模型对终端内存的占用,天玑9300支持在终端运行10亿、70亿、130亿参数的AI大模型。据联发科技官方称,天玑9300成功运行了330亿参数的AI大模型。

APU 790还支持生成式AI模型端侧“技能扩充”技术NeuroPilot Fusion,可以基于基础大模型持续在端侧进行低秩自适应(LoRA,Low-Rank Adaptation)融合,扩展基础大模型的能力。

联发科的AI开发平台NeuroPilot支持Android、Meta Llama 2、百度文心一言大模型、百川智能百川大模型等主流AI大模型,可以让开发者在端侧部署多模态生成式AI应用,实现文字、图像、音乐等方面的终端侧生成式AI创新。

二、AI语义分割视频引擎,逐帧优化、光学防抖

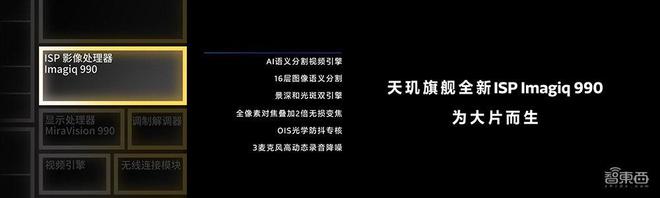

天玑9300的ISP影像处理器是Imagiq 990,支持AI语义分割视频引擎,可以进行16层图像语意分割,对捕捉到的画面色彩、纹理、噪点以及亮度进行实时逐帧优化,视频录制的画面明亮感、锐利度和细节丰富程度得到提升。

天玑9300还支持景深和光斑双引擎、OIS光学防抖专核、全像素对焦叠加2倍无损变焦,在防抖运算速度和成片率、光影效果上有不同程度提升。

三、动态收音噪声分离,AI景深画质引擎,视听升级

在移动显示上,天玑9300集成联发科技MiraVision 990移动显示处理器,支持180Hz WQHD和120Hz 4K显示,以及折叠屏形态的终端设备双屏显示。搭载AI景深画质引擎,实现了实时侦测主要物体和背景图像。

同时,天玑9300搭载联发科技第二代硬件光线追踪引擎,支持60FPS高流畅度的光线追踪,全局光照特效实现游戏主机级别。联发科的MAGT游戏自适应调控技术也升级成为“星速引擎”。

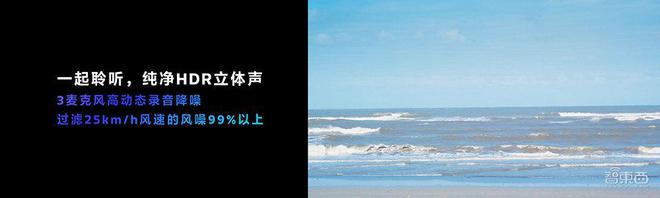

在音频降噪上,天玑9300支持3个麦克风高动态录音降噪,具有动态收音能力,运用噪声分离技术过滤风噪等环境噪音。

除此之外,在网络通信和数据安全上,天玑9300与天玑9200也有不同。

网络通信上,天玑9300集成5G调制解调器,支持Sub-6GHz四载波聚合(4CC-CA)和多制式双卡双通,搭载联发科5G UltraSave 3.0+省电技术,降低 5G 通信功耗。并与AI融合支持情境感知功能。

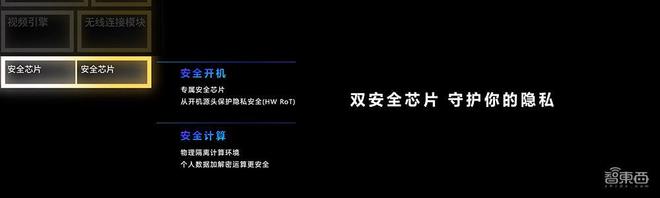

数据安全上,天玑9300配备了新的安全启动芯片、隔离的安全计算环境和Armv9的内存标记扩展,可以帮助开发人员避免内存漏洞利用,实现安全的用户使用环境和开发环境。

结语:AI芯片混战,提升性能、优化用户体验是关键

随着人工智能技术的不断发展,越来越多的企业开始涉足AI芯片领域,AI芯片市场在不断发展与创新,新的芯片架构和技术也在不断涌现,形成了一场激烈的“AI芯片混战”。

从此次联发科发布的新旗舰芯片来看,天玑9300采用全大核架构设计,无论是开发平台支持多种主流大模型,还是支持AI语义分割视频引擎、AI景深画质引擎,天玑9300的各方面优化都离不开AI,也都离不开AI功能带来的用户体验升级。

可见,一个优秀的芯片不仅需要具备高性能,还需要让用户感到操作简单、使用方便,并且在日常使用的多种场景中感受到性能提升带来的体验变化。在AI芯片的竞争中,提升性能和优化用户体验是关键。